Latch Vs Flip Flopblasterfasr

Latches take less gates (less power) to implement than flip-flops. D-FF is built from two latches. They are in master slave configuration. Latch may be clocked or clock less. But flip flop is always clocked. For a transparent latch generally D to Q propagation delay is considered while for a flop clock to Q and setup and hold time. So, gated S-R latch is also called clocked S-R Flip flop or synchronous S-R latch.Since this latch responds to the applied inputs only when the level of the clock pulse is high, this type of flip-flop is also called level triggered flip flop. The logical circuit of a Gated SR Latch or Clocked SR Flip-Flop is shown below. A latch is Level sensitive: Output changes whenever clock/Enable is high (or low) A common implementation of a flip-flop is a pair of latches (Master/Slave flop). Latches are sometimes called “transparent latches”, because they are transparent (input directly connected to output) when the clock is high.

Latches are faster, flip flops are slower. Latch is sensitive to glitches on enable pin, whereas flip-flop i s immune to glitches. Latches take less gates (less power) to implement than flip -flops. D-FF is built from two latches. They are in master slave configuration. Latch may be clocked or clock less.

Both latches and flip-flops are circuit elements whose output depends not only on thepresent inputs, but also on previous inputs and outputs.

- They both are hence referred as 'sequential' elements.

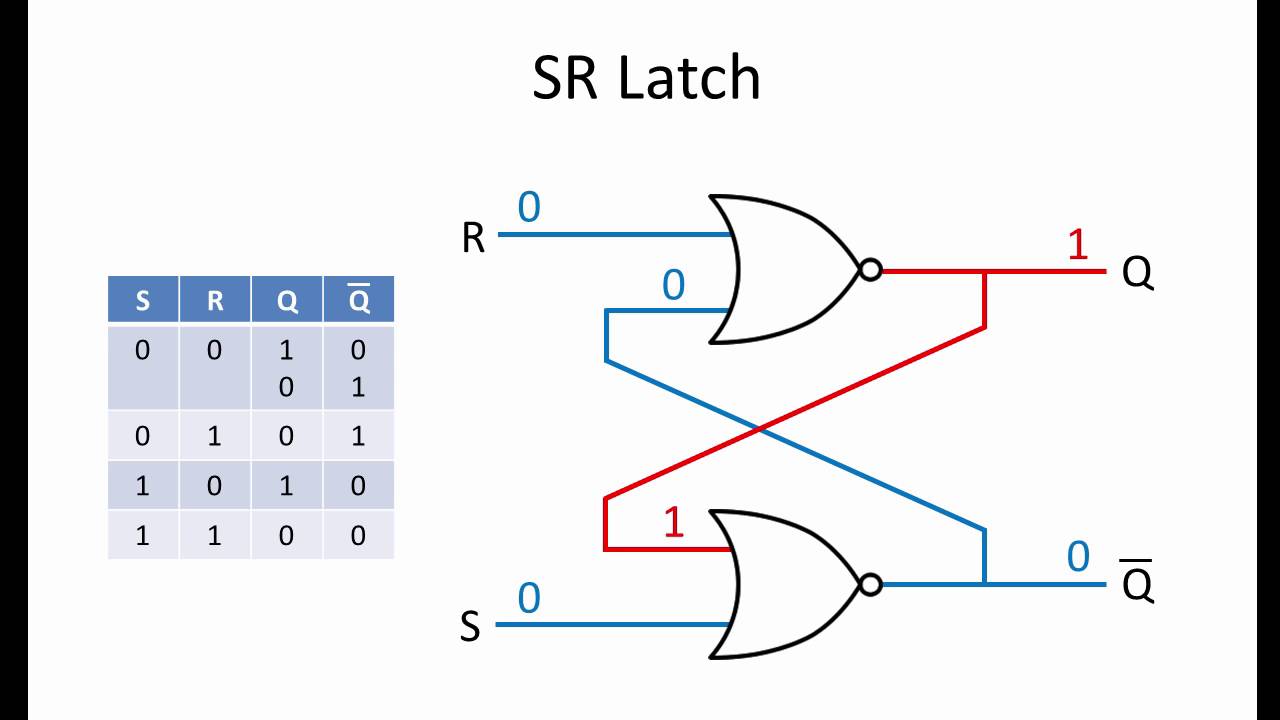

- In electronics, a latch, is a kind of bistable multi vibrator, an electronic circuit which has two stable states and thereby can store one bit of of information. Today the word is mainly used for simple transparent storage elements, while slightly more advanced non-transparent (or clocked) devices are described as flip-flops. Informally, as this distinction is quite new, the two words are sometimes used interchangeably. [wiki]

- In digital circuits, a flip-flop is a kind of bistable multi vibrator, an electronic circuit which has two stable states and thereby is capable of serving as one bit of memory.

- Today, the term flip-flop has come to generally denote non-transparent (clocked or edge-triggered) devices, while the simpler transparent ones are often referred to as latches.[wiki]

- A flip-flop is controlled by (usually) one or two control signals and/or a gate or clock signal.

- Latches are level sensitive i.e. the output captures the input when the clock signal is high, so as long as the clock is logic 1, the output can change if the input also changes.

- Flip-Flops are edge sensitive i.e. flip flop will store the input only when there is a rising or falling edge of the clock.

- A positive level latch is transparent to the positive level(enable), and it latches the final input before it is changing its level(i.e. before enable goes to '0' or before the clock goes to -ve level.)

- A positive edge flop will have its output effective when the clock input changes from '0' to '1' state ('1' to '0' for negative edge flop) only.

- Latches are faster, flip flops are slower.

- Latch is sensitive to glitches on enable pin, whereas flip-flop is immune to glitches.

- Latches take less gates (less power) to implement than flip-flops.

- D-FF is built from two latches. They are in master slave configuration.

- Latch may be clocked or clock less. But flip flop is always clocked.

- For a transparent latch generally D to Q propagation delay is considered while for a flop clock to Q and setup and hold time are very important.

Introduction

On this page you will find a number of MyHDL descriptions of flip-flops andlatches.

Typically, you wouldn't describe flip-flops and latches as individual modules.Rather, they can be inferred from higher-level RTL description by a synthesistool. However, as these circuits are small and widely known, they are wellsuited to explain basic MyHDL usage and to compare MyHDL with other solutions.

D flip-flop

Specification

The basic D flip-flop is a sequential device that transfers the value of thed input to the q output on every rising edge of the clock clk.

Description

Here is the description of a D flip-flop in MyHDL:

Simulation

Let's write a small test bench to simulate the design:

Function test_dff creates an instance of the D flip-flop, and adds a clockgenerator and a random stimulus generator around it.

Function simulate simulates the test bench. Note how the MyHDL functiontraceSignals is used to create the test bench instance (instead of callingtest_dff directly). As a result, a signal trace file will be created duringsimulation. This file can be inspecting in a waveform viewer. As a verificationmethod, inspecting waveforms has its drawbacks, but it can be very effective todebug small designs.

Here's a screen shot of the simulation waveforms:

Automatic conversion to Verilog

With MyHDL's toVerilog function, a D flip-flop instance can be converted toVerilog code:

This is the resulting Verilog code:

D flip-flop with asynchronous reset

Specification

One of the most useful sequential building blocks is a D flip-flop with anadditional asynchronous reset pin. When the reset is not active, it operates asa basic D flip-flop as in the previous section. When the reset pin is active,the output is held to zero. Typically, the reset pin is active low.

Description

Here is the description:

Simulation

Here is a test bench for the design:

Compared to the test bench for the basic D flip-flop, there is an additionalreset generator, that generates reset pulses at random moments and with arandom duration.

Here is a screen shot of the waveforms:

Automatic conversion to Verilog

The design can be converted to Verilog as follows:

The result looks like this:

Latch

Specification

A basic latch is a sequential device with an input, and output and a controlgate pin. When the gate is open, the output follows the input combinatorially.When it is closed, the output keeps its value.

Description

The following code describes a latch:

Note the usage of the always_comb decorator. This is somewhat of a misnomer.(The name comes from a similar construct in SystemVerilog). It doesn't mean thegenerator describes a circuit that is necessarily combinatorial, but merelythat it triggers whenever one of the input signals changes.

Simulation

Here is a test bench to simulate the latch:

In addition to the latch instance, the test bench creates a random datagenerator for the input and for the controlling gate.

Here is a screen shot of the simulation waveforms:

Automatic conversion to Verilog

We can convert the design as follows:

Latch Vs Flip Flop

Here is the result:

D Flip Flops

Note that when the toVerilog function converts the always_comb decorator,it infers which signals are used as inputs to the always block